Von Neumann Architecture

Prior to von Neumann

- Computers were built for specific tasks

- Programs were hard-wired into the computer

- You had to either build a new computer or rewire the existing one to change the program

John von Neumann

- Hungarian-American mathematician and physicist

- Member of the Manhattan Project

- Interested in how to build a general-purpose computer

Preliminary Discussion of the Logical Design of an Electronic Computing Instrument

-- Arthur W. Burks

-- Herman H. Goldstine

-- John von Neumann

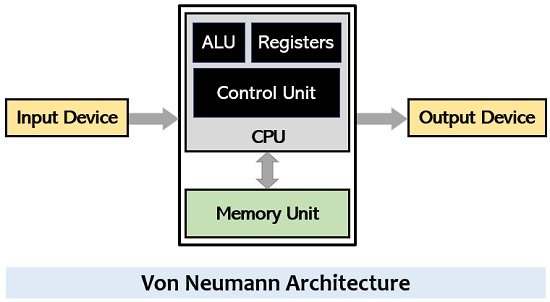

Components of the von Neumann Architecture

Input/Output (I/O)

- Devices that allow the computer to interact with the outside world

-

Examples:

- IN: keyboards, mice, touchscreens, file storage (load a file, e.g. a program)

- OUT: monitors, speakers, printers, file storage (write to a file)

- In von Neumann's time it may have included punch cards or paper tape

Memory

- Stores data and instructions that the CPU needs to operate

- Today if you hear the word "memory" we are referring to RAM. We call hard drives "storage" or "secondary storage".

- In von Neumann's time it may have included vacuum tubes

Central Processing Unit (CPU)

- The "brain" of the computer

- Where instructions are executed

-

Has three main components:

- Control Unit

- Arithmetic Logic Unit (ALU)

- Registers

Registers

- Small amount of storage on the CPU itself

- Extremely fast because of proximity to CPU components

- Every operation in the CPU involves fist moving data to and from registers

- There are reserved "special" registers as well as general purpose registers

Control Unit

- "Manager" of the CPU

- Manages the flow of data and instructions within the computer

Arithmetic Logic Unit (ALU)

- "Worker" of the CPU

-

Performs arithmetic and logical operations

- Arithmetic: addition, subtraction, multiplication, division

- Logical: AND, OR, NOT, XOR

- Comparison: greater than, less than, equal to

- etc.

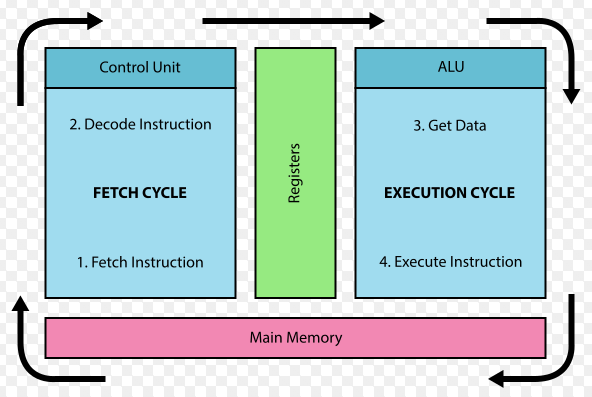

Fetch Decode Execute Cycle

The CPU will pick off one instruction at a time from memory and execute it. This is called the Fetch Decode Execute Cycle.

-

Fetch:

- Move the instruction from memory to a special instruction register in the CPU.

- This instruction is determined by the value in the program counter register.

- The program counter is then incremented so that the next instruction can be fetched.

-

Decode:

- The control unit reads the instruction and determines what to do.

- It preps the ALU and other components for the operation that will come next.

-

Execute:

- The ALU performs the operation on the data in the registers.

- The intermediate result is stored in a special register called the accumulator.

By shuffling data between memory and registers, the CPU can perform all of the operations necessary to run a program.

We discuss these instructions in more detail in the "Evolution of Programming" page.

Slight correction to the video: the program counter is incremented immediately after the instruction is fetched, not after it is executed.

The "JUMP 1" instruction does not skip the execution cycle. It updates the program counter on its execution.