Logic Gates

For an online logic gate sandbox, see: Logic.ly.

Foundations

-

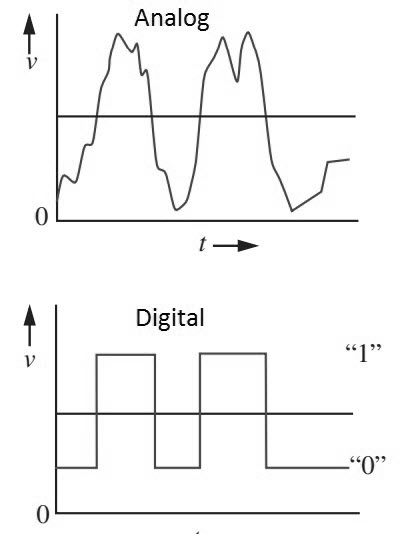

Computers recognize only two states, based on the presence or absence of an electrical signal.

- High voltage = 1 = true

- Low voltage = 0 = false

-

A logic gate is a device that performs a logical operation on one or more binary inputs and produces a single binary output.

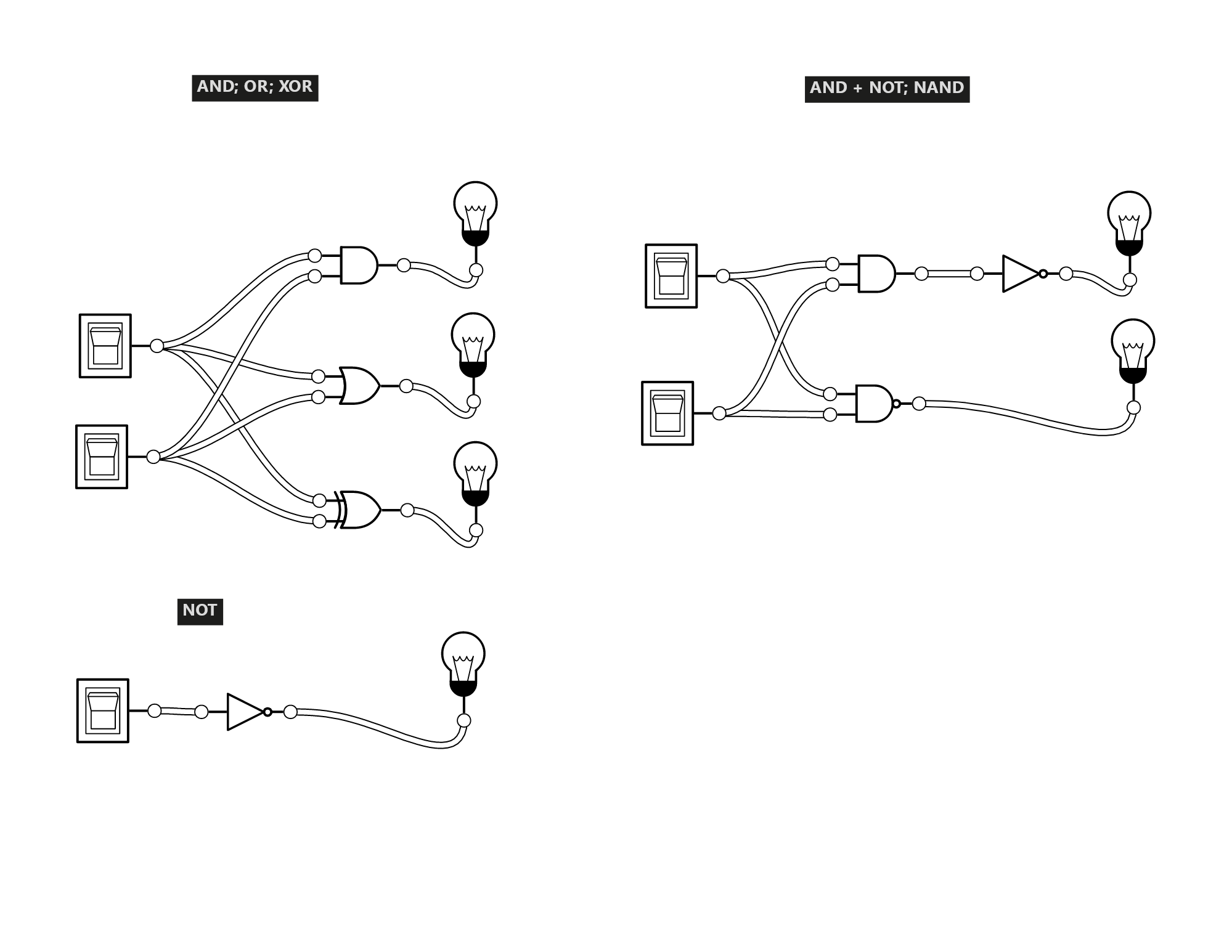

Basic Gates

The logical connectives that we've learned so far have corresponding logic gates.

The truth table for each gate matches the truth table for the corresponding logical connective.

Let's try out some basic gates in Logic.ly.

Circuits

We can combine logic gates to create circuits.

These circuits can do things like:

- Arithmetic (addition, subtraction, etc.)

- Comparison (greater than, less than, equal)

- Memory storage

- ...

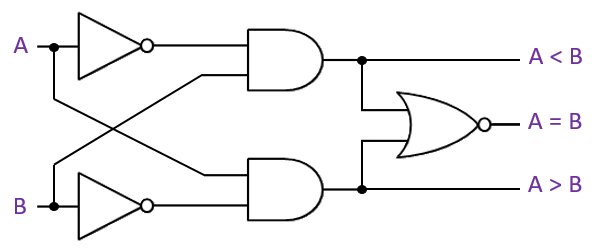

Comparing Values

A magnitude comparator is a type of combinational circuit that compares two numbers.

One bit magnitude comparator:

One Bit Magnitude Comparator - Logicly

Assume that A = 1, B = 1.

For each output:

a) Translate the circuit into a boolean expression.

b) Plug the above values into the circuit and solve.

Hint: Remember your truth tables and the fact that 1 = true and 0 = false.

Output: A < B

a) ¬A ∧ B

b) 0 ∧ 1 = False

Output: A > B

a) A ∧ ¬B

b) 1 ∧ 0 = False

Output: A = B

a)

- ¬( ¬A ∧ B ∨ A ∧ ¬B )

- A ∨ ¬B ∧ ¬A ∨ B

b)

- 1 ∨ (0 ∧ 0) ∨ 1

- 1 ∨ 0 ∨ 1 = True

Keeping Values in Memory

SR (Set-Reset) Latch

The SR latch is a simple form of flip-flop that can store one bit of information as memory so that it isn't lost when the clock signal changes.

When in the hold state, the outputs remain the same.

They will only change when either the set or reset input is activated.

Circuit:

Demo: Building an Arm and Click Camera

Scenario:

In this demo, we'll build a system that requires the user to arm a camera before taking a picture.

The camera has three buttons:

- Photo - Takes a picture

- Arm - Arms the camera

- Reset - Resets the camera to unarmed

Components

- An SR latch will store the "armed" state of the camera.

- We will combine the SR latch with the photo button via an AND gate to allow the camera to take a picture only when armed.

- The reset button will be connected to the SR latch to clear the memory and disarm the camera.

Circuit:

Synchronizing Information

In digital circuits, we need to be precise about when information is updated.

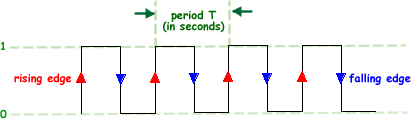

The Clock

The clock is a special signal that is used to synchronize the operations of a computer. For now, we just need to know:

- The clock pulses electrical signals at regular intervals.

- A high signal is called a rising edge. This indicates "true", or 1.

- A low signal is called a falling edge. This indicates "false", or 0.

- One up and down pulse (taken together) is called a clock cycle.

SR Flip-Flop

The SR flip-flop extends the SR latch by adding a clock signal.

This signal allows the flip-flop to store information only when the clock signal changes.

Inputs / Outputs:

- C = Clock signal

- S = Set signal

- R = Reset signal

- Q = Output

Truth Table:

Same as above, except now the output can only change on a rising edge (uptick) of the clock signal.

Circuit:

Demo: Building a Hold Activated Button

Scenario:

In this demo, we'll build a system that requires the user to hold a button (S) for a full clock cycle before a light turns on.

We will measure the time using the system clock (C). If the button is held for one clock cycle (rise and fall edge), the light will turn on.

There is a reset button (R) that can be used to turn off the light.

Components:

- The "on" button and a rising clock signal will set a memory bit using SR flip-flop.

- The "on" button and a falling clock signal will set a memory bit using another SR flip-flop.

- We will use an AND gate to combine the two signals and turn on the light.

- We will hook up the reset button to the two SR latches to clear memory and turn off the light.

Circuit: